# **KEELOQ<sup>®</sup> Code Hopping Encoder with UHF ASK/FSK Transmitter**

#### General:

- Combination Keelog encoder and synthesized UHF ASK/FSK transmitter in a single package

- Operates on a single lithium coin cell

- <200 nA typical standby current

- 4.8 to 11.5 mA transmit current

- 2.2 to 5.5V operation

- · Integrated solution with minimum external parts

- Separate pin-outs for KEELOQ encoder and RF transmitter provides for design flexibility

### **Code Hopping Encoder:**

- Programmable minimum code word completion

- Battery low signal transmitted to receiver with programmable threshold

- Non-volatile EEPROM storage of synchronization data

- Easy to use EEPROM programming interface

- · PWM or Manchester modulation

- Selectable encoder data rate 417 to 3334 bps

- · On-chip tunable encoder oscillator

- RF Enable output for transmitter control

- Button inputs have internal pull-down resistors

- · Elapsed time and button queuing options

- Current limiting on LED output

- 2-bit CRC for error detection

### **UHF ASK/FSK Transmitter:**

- Conforms to US FCC Part 15.231 regulations and European ERC 70-03E and EN 300 220-1 requirements

- VCO phase locked to quartz crystal reference; allows narrow receiver bandwidth to maximize range and interference immunity

- Crystal frequency divide by 4 output (CLKOUT)

- Transmit frequency range (310 440 MHz) set by Crystal frequency

- ASK Modulation

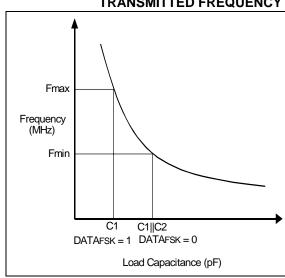

- FSK Modulation through crystal pulling (rfHCS362F)

- Adjustable output power: -12 dBm to +2 dBm

- Differential output configurable for single or double ended loop antenna

- · Automatic power amplifier inhibit until PLL lock

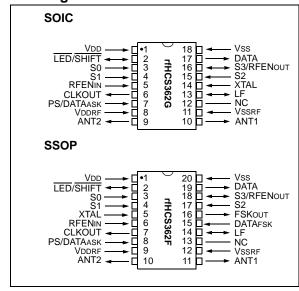

### Pin Diagrams

### Security:

- Programmable 28/32-bit serial number

- Two programmable 64-bit encryption keys

- Programmable 60-bit seed

- Each 69-bit transmission is unique with 32 bits of hopping code

- · Encryption keys are read protected

### **Applications:**

- · Automotive Remote Keyless Entry (RKE) systems

- · Automotive alarm systems

- · Automotive immobilizers

- Community gate and garage door openers

- · Identity tokens with usage counters

- Burglar alarm systems

- · Building access

|            | Features        |          |             |  |

|------------|-----------------|----------|-------------|--|

| Device     | Encrypt<br>Keys | Encoding | Transmitter |  |

| rfHCS362AG | 2 x 64          | PWM/MAN  | ASK         |  |

| rfHCS362AF | 2 x 64          | PWM/MAN  | ASK/FSK     |  |

| 10   | Constal Pagarintian                            | 2  |

|------|------------------------------------------------|----|

| 1.0  | General Description                            | ర  |

| 2.0  | Device Description                             | 9  |

| 3.0  | General Description                            | 13 |

| 4.0  | EEPROM Memory Organization                     | 21 |

| 5.0  | Programming the rfHCS362G/362F                 | 27 |

| 6.0  | UHF ASK/FSK Transmitter                        | 29 |

| 7.0  | Integrating the rfHCS362G/362F into the System | 37 |

| 8.0  | Development Support                            | 41 |

| 9.0  | Electrical Characteristics                     | 43 |

| 10.0 | DC Characteristics                             | 45 |

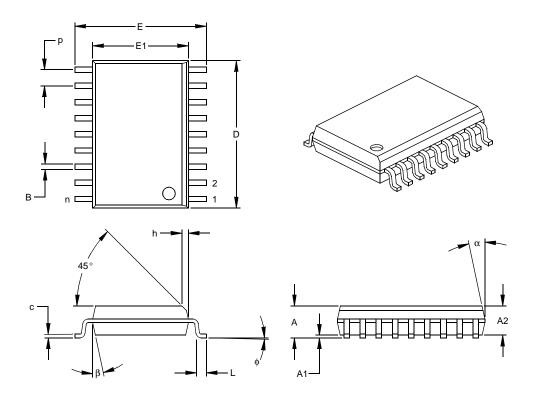

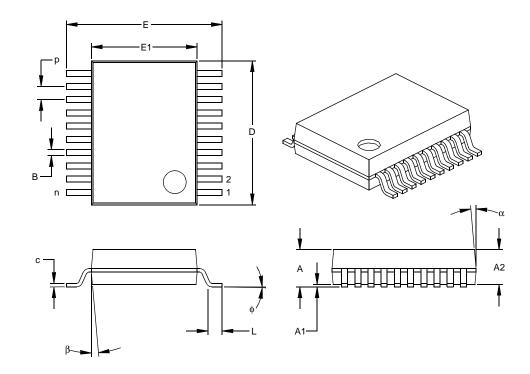

| 11.0 | Packaging Information                          | 51 |

| App  | endix A: Data Sheet Revision History           | 54 |

| On-I | ine Support                                    | 55 |

| Rea  | der Response                                   | 56 |

|      | S362G/362F Product Identification System       |    |

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### Customer Notification System

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

### 1.0 GENERAL DESCRIPTION

The rfHCS362G/362F is a code hopping encoder plus UHF transmitter designed for secure wireless command and control systems. The rfHCS362G/362F utilizes the KEELOQ® code hopping technology which incorporates high security in a small package outline at a low cost to make this device well suited for unidirectional remote keyless entry systems and access control systems.

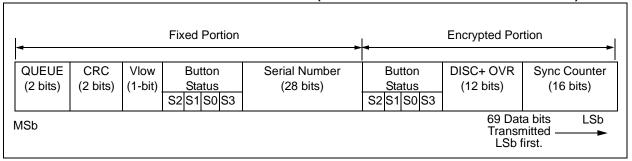

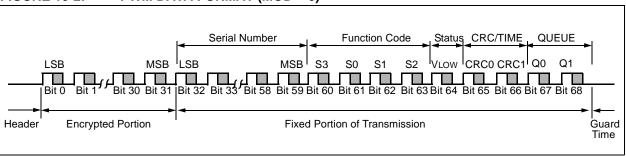

The rfHCS362G/362F combines a 32-bit hopping code generated by a nonlinear encryption algorithm with a 28/32-bit serial number and 9/5 status bits to create a 69-bit transmission stream. The length of the transmission strongly resists the threat of code scanning. The code hopping mechanism makes each transmission unique, thus rendering code capture and resend (code grabbing) schemes virtually useless.

The encryption key, serial number and configuration data are stored in an EEPROM array which is not accessible via any external connection. The EEPROM data is programmable but read protected. The data can be verified only after an automatic erase and programming operation. This protects against attempts to gain access to keys or manipulate synchronization values. The rfHCS362G/362F provides an easy to use serial interface for programming the necessary keys, system parameters and configuration data.

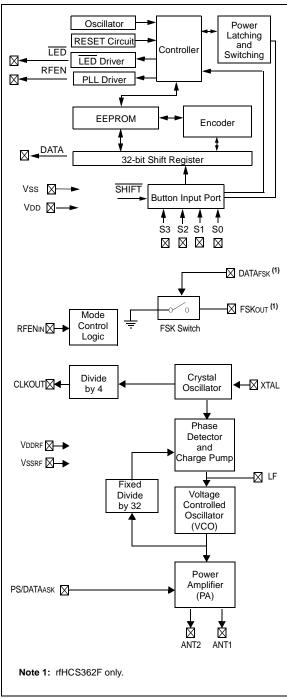

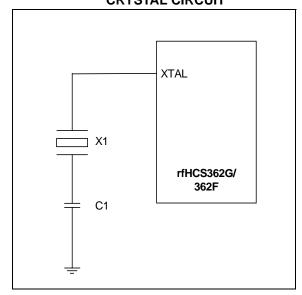

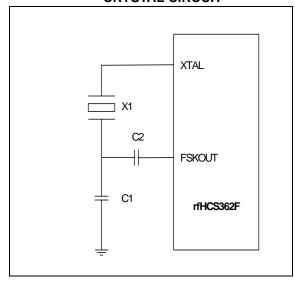

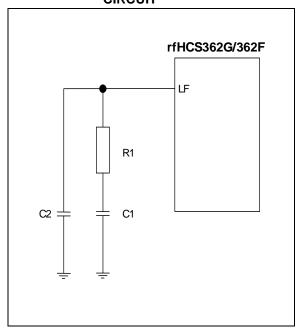

The transmitter is a fully integrated UHF ASK/FSK transmitter consisting of crystal oscillator, Phase-Locked Loop (PLL), open-collector differential-output Power Amplifier (PA), and mode control logic. External components consist of bypass capacitors, crystal, and PLL loop filter. There are no internal electrical connections between the encoder and the transmitter. The encoder oscillator is independent from the transmitter crystal oscillator.

The rfHCS362G is capable of Amplitude Shift Keying (ASK) modulation by turning the PA on and off. The rfHCS362F is capable of ASK or Frequency Shift Keying (FSK) modulation by employing an internal FSK switch to pull the transmitter crystal via a second load capacitor.

The rfHCS362G/362F is a single channel device. The transmit frequency is fixed and set by an external reference crystal. Transmit frequencies in the range of 310 to 440 MHz can be selected. Output drive is an open-collector differential amplifier. The differential output is well suited for loop antennas. Output power is adjustable from +2 dBm to -12 dBm in six discrete steps.

The rfHCS362G/362F are radio frequency (RF) emitting devices. Wireless RF devices are governed by a country's regulating agency. For example, in the United States it is the Federal Communications Committee (FCC) and in Europe it is the European Conference of Postal and Telecommunications Administrations

(CEPT). It is the responsibility of the designer to ensure that their end product conforms to rules and regulations of the country of use and/or sale.

RF devices require correct board level implementation in order to meet regulatory requirements. Layout considerations are given in Section 6.0 UHF ASK/FSK Transmitter.

### 1.1 Important Terms

The following is a list of key terms used throughout this data sheet. For additional information on KEELOQ and Code Hopping refer to Technical Brief 3 (TB003).

- RKE Remote Keyless Entry

- Button Status Indicates what button input(s) activated the transmission. Encompasses the 4 button status bits S3, S2, S1 and S0 (Figure 3-6).

- Code Hopping A method by which a code, viewed externally to the system, appears to change unpredictably each time it is transmitted.

- Code word A block of data that is repeatedly transmitted upon button activation (Figure 3-6).

- **Transmission** A data stream consisting of repeating code words (Figure 10-1).

- Encryption key A unique and secret 64-bit number used to encrypt and decrypt data. In a symmetrical block cipher such as the KEELOQ algorithm, the encryption and decryption keys are equal and will be referred to generally as the encryption key.

- Encoder A device that generates and encodes data

- Encryption Algorithm A recipe whereby data is scrambled using a encryption key. The data can only be interpreted by the respective decryption algorithm using the same encryption key.

- Decoder A device that decodes data received from an encoder.

- Decryption algorithm A recipe whereby data scrambled by an encryption algorithm can be unscrambled using the same encryption key.

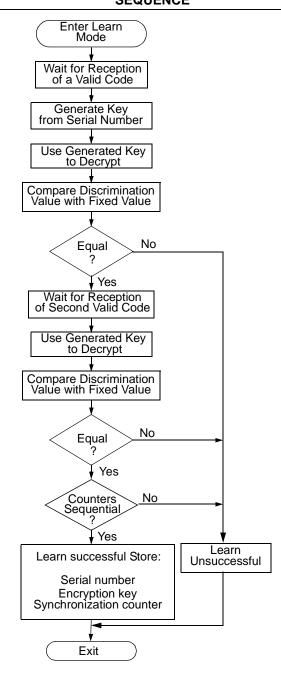

- Learn Learning involves the receiver calculating

the transmitter's appropriate encryption key,

decrypting the received hopping code and storing

the serial number, synchronization counter value

and encryption key in EEPROM. The KEELOQ

product family facilitates several learning strategies to be implemented on the decoder. The following are examples of what can be done.

### - Simple Learning

The receiver uses a fixed encryption key, common to all components of all systems by the same manufacturer, to decrypt the received code word's encrypted portion.

#### - Normal Learning

The receiver uses information transmitted during normal operation to derive the encryption key and decrypt the received code word's encrypted portion.

### - Secure Learn

The transmitter is activated through a special button combination to transmit a stored 60-bit seed value used to generate the transmitter's encryption key. The receiver uses this seed value to derive the same encryption key and decrypt the received code word's encrypted portion.

Manufacturer's code – A unique and secret 64bit number used to generate unique encoder encryption keys. Each encoder is programmed with a encryption key that is a function of the manufacturer's code. Each decoder is programmed with the manufacturer code itself.

### 1.2 Applications

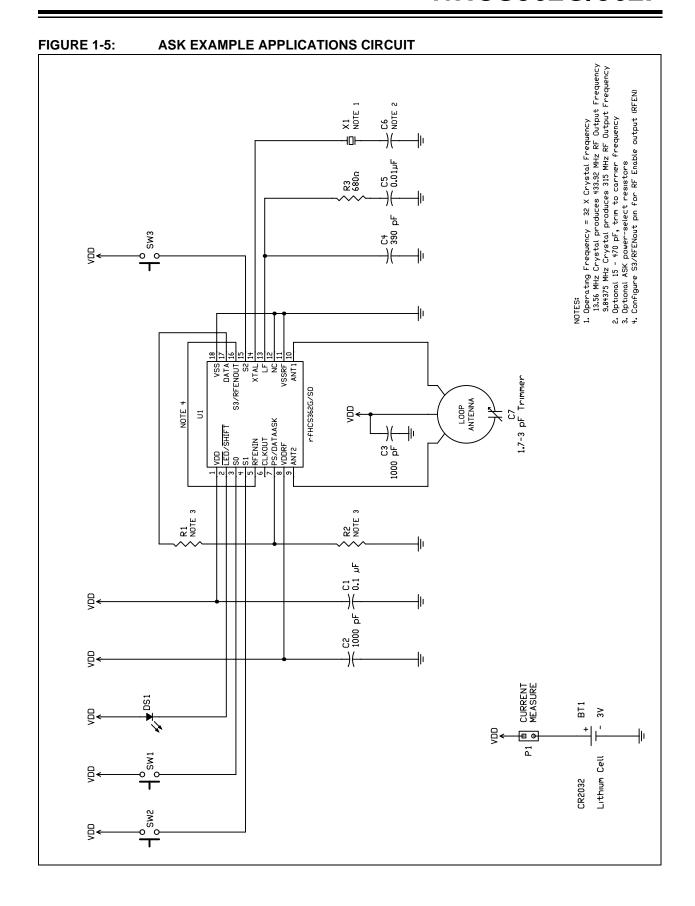

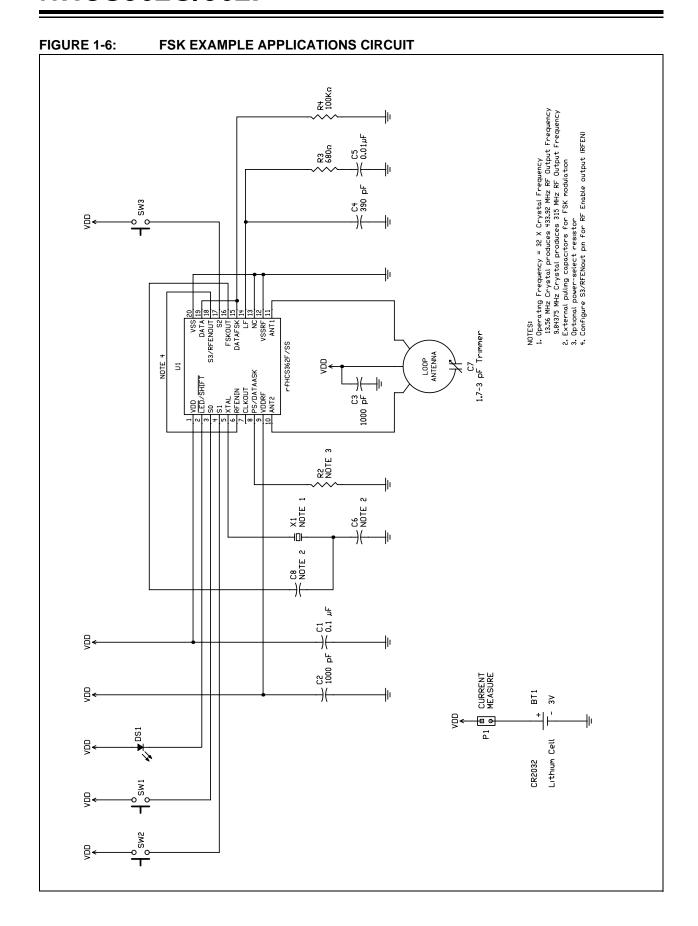

The rfHCS362G/362F is suited for secure wireless remote control applications. The EEPROM technology makes customizing application programs (transmitter codes, appliance settings, etc.) extremely fast and convenient. The small footprint packages are suitable for applications with space limitations. Low-cost, low-power, high performance, ease of use and I/O flexibility make the rfHCS362G/362F very versatile. Typical application circuits are shown in Figure 1-5 and Figure 1-6.

Most low-end keyless entry transmitters are given a fixed identification code that is transmitted every time a button is pushed. The number of unique identification codes in a low-end system is usually a relatively small number. These shortcomings provide an opportunity for a sophisticated thief to create a device that 'grabs' a transmission and retransmits it later, or a device that quickly 'scans' all possible identification codes until the correct one is found.

The rfHCS362G/362F, on the other hand, employs the KEELOQ code hopping technology coupled with a transmission length of 66 bits to virtually eliminate the use of code 'grabbing' or code 'scanning'. The high security level of the rfHCS362G/362F is based on patented technology. A block cipher based on a block length of 32 bits and a key length of 64 bits is used. The algorithm obscures the information in such a way that even if the transmission information (before coding) differs by only one bit from that of the previous transmission, the next coded transmission will be completely different. Statistically, if only one bit in the 32-bit string of information changes, approximately 50 percent of the coded transmission bits will change.

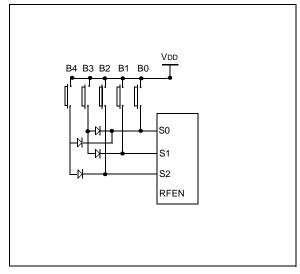

### FIGURE 1-1: ADDITIONAL BUTTON INPUTS

Up to 7 button inputs can be implemented making them look like a binary value to the 3 Sx inputs. This is done with switching diodes as shown in Figure 1-1. The disadvantage is that simultaneously pressed buttons now appear as if a single button is pressed.

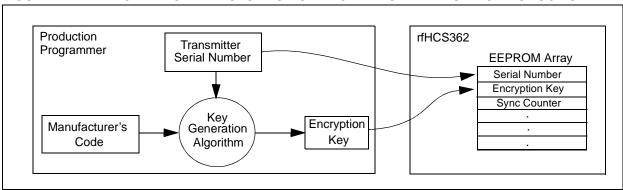

The rfHCS362G/362F has a small EEPROM array which must be loaded with several parameters before use. These are most often programmed by the manufacturer at the time of production. The most important of these are:

- A 28-bit serial number, typically unique for every encoder

- · An encryption key

- An initial 16-bit synchronization value

- A 16-bit configuration value

The encryption key generation typically inputs the transmitter serial number and 64-bit manufacturer's code into the key generation algorithm (Figure 1-2). The manufacturer's code is chosen by the system manufacturer and must be carefully controlled as it is a pivotal part of the overall system security.

The 16-bit synchronization counter is the basis behind the transmitted code word changing for each transmission; it increments each time a button is pressed. Due to the code hopping algorithm's complexity, each increment of the synchronization value results in about 50% of the bits changing in the transmitted code word.

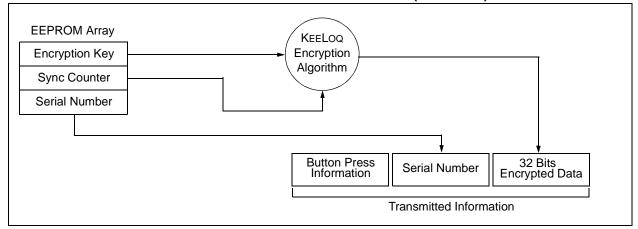

Figure 1-3 shows how the key values in EEPROM are used in the encoder. Once the encoder detects a button press, it reads the button inputs and updates the synchronization counter. The synchronization counter and encryption key are input to the encryption algorithm and the output is 32 bits of encrypted information. This data will change with every button press, its value appearing externally to 'randomly hop around', hence it is referred to as the hopping portion of the code word. The 32-bit hopping code is combined with the button information and serial number to form the code word transmitted to the receiver. The code word format is explained in greater detail in Section 3.1.

A receiver may use any type of controller as a decoder, but it is typically a microcontroller with compatible firmware that allows the decoder to operate in conjunction with an rfHCS362G/362F based transmitter. Section 7.0 provides detail on integrating the rfHCS362G/362F into a system.

A transmitter must first be 'learned' by the receiver before its use is allowed in the system. Learning includes calculating the transmitter's appropriate encryption key, decrypting the received hopping code and storing the serial number, synchronization counter value and encryption key in EEPROM.

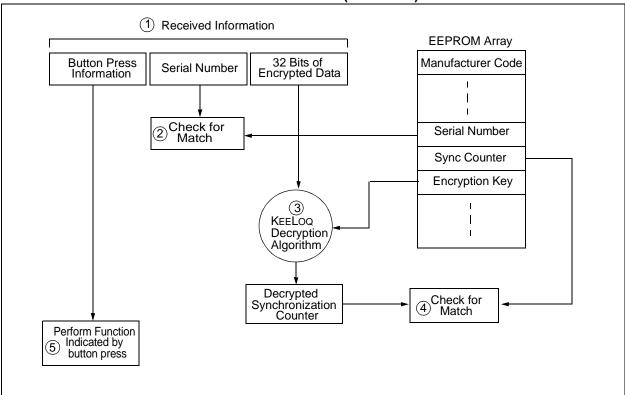

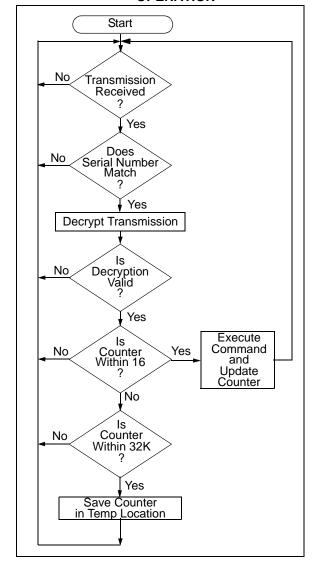

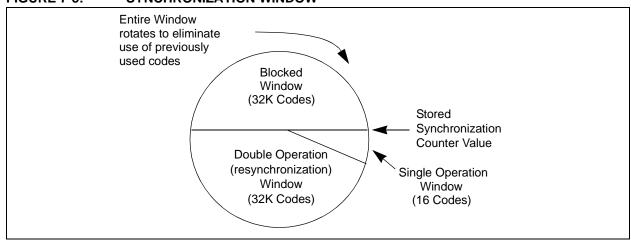

In normal operation, each received message of valid format is evaluated. The serial number is used to determine if it is from a learned transmitter. If from a learned transmitter, the message is decrypted and the synchronization counter is verified. Finally, the button status is checked to see what operation is requested. Figure 1-4 shows the relationship between some of the values stored by the receiver and the values received from the transmitter.

FIGURE 1-2: CREATION AND STORAGE OF ENCRYPTION KEY DURING PRODUCTION

FIGURE 1-3: BUILDING THE TRANSMITTED CODE WORD (ENCODER)

FIGURE 1-4: BASIC OPERATION OF RECEIVER (DECODER)

NOTE: Circled numbers indicate the order of execution.

### 2.0 DEVICE DESCRIPTION

The block diagram in Figure 2-1 shows the internal configuration with the top half representing the encoder and the bottom half the UHF transmitter. Note that connections between the encoder and transmitter are made external to the device for more versability.

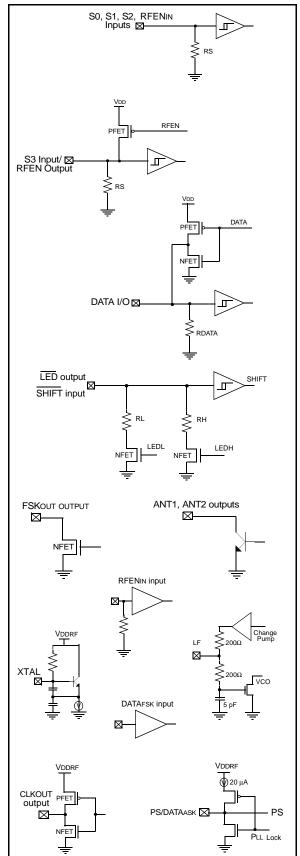

Typical application circuits are shown in Figure 1-5 and Figure 1-6. The rfHCS362G/362F requires only the addition of push button switches and few external components for use as a transmitter in your security application. See Table 2-1 for pinout description. Figure 2-2 shows the device I/O circuits.

FIGURE 2-1: rfHCS362 BLOCK DIAGRAM

TABLE 2-1: rfHCS362G/362F PINOUT DESCRIPTION

| Name       | SOIC<br>Pin # | SSOP<br>Pin # | I/O/P<br>Type | Description                                                                                                         |  |

|------------|---------------|---------------|---------------|---------------------------------------------------------------------------------------------------------------------|--|

| ANT1       | 10            | 11            | 0             | Antenna connection to differential power amplifier output, open collector.                                          |  |

| ANT2       | 9             | 10            | 0             | Antenna connection to differential power amplifier output, open collector.                                          |  |

| CLKOUT     | 6             | 7             | 0             | Clock output.                                                                                                       |  |

| DATA       | 17            | 19            | I/O           | Encoder data output pin or serial programming.                                                                      |  |

| DATAFSK    |               | 15            | I             | FSK data input.                                                                                                     |  |

| FSKout     |               | 16            | 0             | FSK crystal pulling output.                                                                                         |  |

| LED/SHIFT  | 2             | 2             | I/O           | Current limited LED driver. Input sampled before LED driven.                                                        |  |

| LF         | 13            | 14            | _             | External loop filter connection. Common node of charge pump output and VCO tuning input.                            |  |

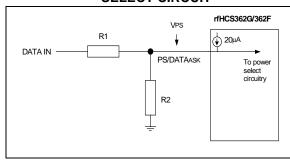

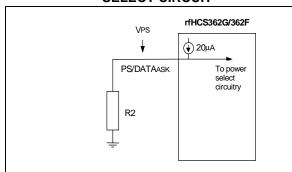

| PS/DATAASK | 7             | 8             | I             | Power select and ASK data input.                                                                                    |  |

| RFENIN     | 5             | 6             | I             | Transmitter and CLKOUT enable. Internal pull-down.                                                                  |  |

| S0         | 3             | 3             | I             | Switch input 0 with internal pull-down.                                                                             |  |

| S1         | 4             | 4             | I             | Switch input 1 with internal pull-down.                                                                             |  |

| S2         | 15            | 17            | I             | Switch input 2 with internal pull-down or Schmitt Trigger clock input during serial programming.                    |  |

| S3/RFEN    | 16            | 18            | I/O           | Switch input 3 with internal pull-down or RF enable output as selected by RFEN option in configuration word SEED_3. |  |

| VDD        | 1             | 1             | Р             | Positive supply for encoder                                                                                         |  |

| VDDRF      | 8             | 9             | Р             | Positive supply for transmitter.                                                                                    |  |

| Vss        | 18            | 20            | Р             | Ground reference for encoder                                                                                        |  |

| VSSRF      | 11            | 12            | Р             | Ground reference for transmitter.                                                                                   |  |

| XTAL       | 14            | 5             | I             | Transmitter crystal connection to Colpitts type crystal oscillator.                                                 |  |

Legend: I = input, O = output, I/O = input/output, P = power

### FIGURE 2-2: I/O CIRCUITS

### 2.1 Encoder Architectural Overview

### 2.1.1 ONBOARD EEPROM

The rfHCS362G/362F has an onboard nonvolatile EEPROM which is used to store user programmable data. The data can be programmed at the time of production and includes the security-related information such as encoder keys, serial numbers, discrimination and seed values. All the security related options are read protected. The rfHCS362G/362F has built-in protection against counter corruption. Before every EEPROM write, the internal circuitry also ensures that the high voltage required to write to the EEPROM is at an acceptable level.

### 2.1.2 INTERNAL RC OSCILLATOR

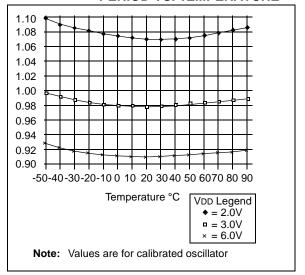

The rfHCS362G/362F has an onboard RC oscillator that controls all the logic output timing characteristics. The oscillator frequency varies within  $\pm 10\%$  of the nominal value (once calibrated over a voltage range of 2V-3.5V or 3.5V-6.3V). All the timing values specified in this document are subject to the oscillator variation.

FIGURE 2-3: TYPICAL rfHCS362G/362F NORMALIZED OSCILLATOR PERIOD VS. TEMPERATURE

### 2.1.3 LOW VOLTAGE DETECTOR

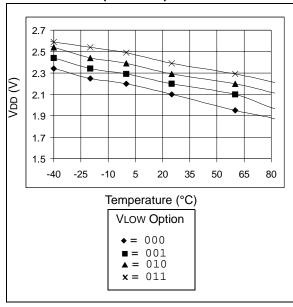

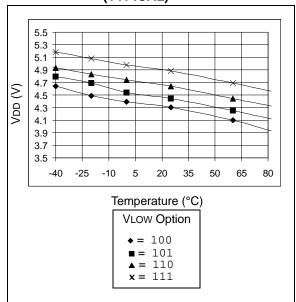

A low battery voltage detector onboard the rfHCS362G/362F can indicate when the operating voltage drops below a predetermined value. There are eight options available depending on the VLOW[0..2] configuration options. The options provided are:

| 000 | - 2.0V | 100 | - | 4.0V |

|-----|--------|-----|---|------|

| 001 | - 2.1V | 101 | - | 4.2V |

| 010 | - 2.2V | 110 | - | 4.4V |

| 011 | - 2.3V | 111 | - | 4.6V |

FIGURE 2-4: rfHCS362 VLow DETECTOR (TYPICAL)

FIGURE 2-5: rfHCS362 VLow DETECTOR (TYPICAL)

The output of the low voltage detector is transmitted in each code word, so the decoder can give an indication to the user that the transmitter battery is low. Operation of the  $\overline{\text{LED}}$  changes as well to further indicate that the battery is low and needs replacing.

### 3.0 ENCODER OPERATION

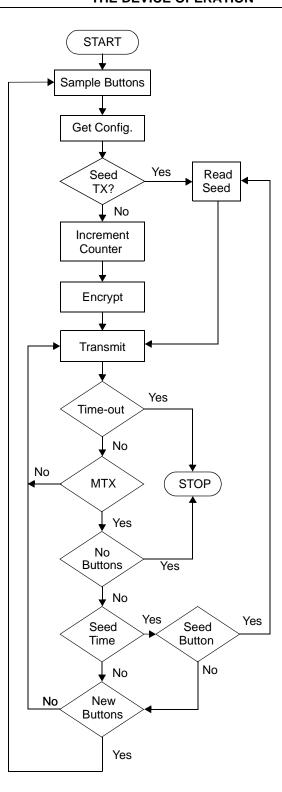

The rfHCS362G/362F will wake-up upon detecting a switch closure and then delay for switch debounce (Figure 3-1). The synchronization information, fixed information and switch information will be encrypted to form the hopping code. The encrypted or hopping code portion of the transmission will change every time a button is pressed, even if the same button is pushed again. Keeping a button pressed for a long time will result in the same code word being transmitted until the button is released or time-out occurs.

The time-out time can be selected with the time-out (TIMOUT[0..1]) configuration option. This option allows the time-out to be disabled or set to  $0.8~s,\,3.2~s$  or 25.6~s. When a time-out occurs, the device will go into SLEEP mode to protect the battery from draining when a button gets stuck.

If in the transmit process, and a new button is pressed, the current code word will be aborted. A new code word will be transmitted and the time-out counter will RESET. If all the buttons are released, the minimum code words will be completed. The minimum code words can be set to 1, 2, 4 or 8 using the Minimum Code Words (MTX[0..1]) configuration option. If the time for transmitting the minimum code words is longer than the time-out time, the device will not complete the minimum code words.

Note: If multiple buttons are pressed and one is released, it will not have any effect on the code word. If no buttons remain pressed the minimum code words will be completed and the power-down will occur.

A code that has been transmitted will not occur again for more than 64K transmissions. This will provide more than 18 years of typical use before a code is repeated based on 10 operations per day. Overflow information programmed into the encoder can be used by the decoder to extend the number of unique transmissions to more than 192K.

FIGURE 3-1: BASIC FLOW DIAGRAM OF THE DEVICE OPERATION

### 3.1 Transmission Modulation Format

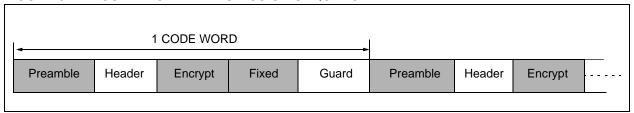

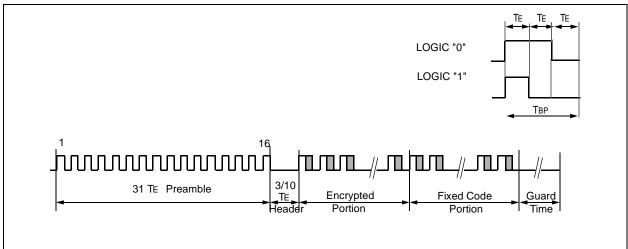

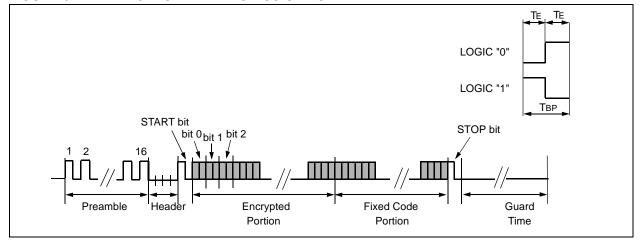

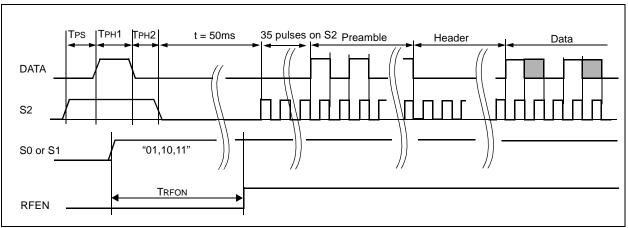

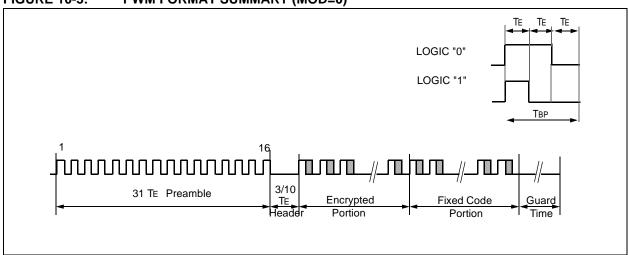

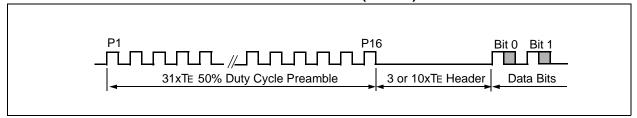

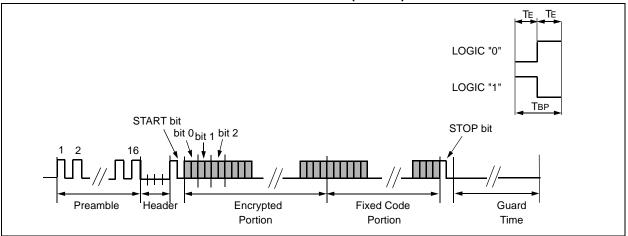

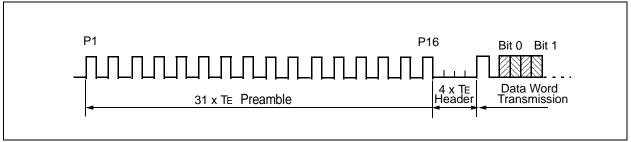

The rfHCS362 transmission is made up of several code words. Each code word consists of a preamble, a header and data (see Figure 3-2).

The code words are separated by a **Guard Time** that can be set to 0 ms, 6.4 ms, 25.6 ms or 76.8 ms with the Guard Time Select (GUARD[0..1]) configuration option. All other timing specifications for the modulation formats are based on a basic timing element (TE). This **Timing Element** can be set to 100  $\mu$ s, 200  $\mu$ s, 400  $\mu$ s or 800  $\mu$ s with the Baud Rate Select (BSEL[0..1])

configuration option. The **Header Time** can be set to 3 TE or 10 TE with the Header Select (HEADER) configuration option.

There are two different modulation formats available on the rfHCS362 that can be set using the Modulation Select (MOD) configuration option:

- Pulse Width Modulation (PWM)

- · Manchester Encoding

Modulation formats are shown in Figure 3-3 and Figure 3-4. Code word data formats are shown in Figure 3-6.

FIGURE 3-2: CODE WORD TRANSMISSION SEQUENCE

FIGURE 3-3: PULSE WIDTH MODULATION TRANSMISSION FORMAT

FIGURE 3-4: MANCHESTER TRANSMISSION FORMAT

#### 3.1.1 CODE HOPPING DATA

The hopping portion is calculated by encrypting the counter, discrimination value and function code with the Encoder Key (KEY). The counter is 16 bits wide. The discrimination value is 10 bits wide. There are 2 counter overflow bits (OVR) that are cleared when the counter wraps to 0. The rest of the 32 bits are made up of the function code also known as the button inputs.

### 3.1.2 FIXED CODE DATA

The 32 bits of fixed code consist of 28 bits of the serial number (SER) and another copy of the function code. This can be changed to contain the whole 32-bit serial number with the Extended Serial Number (XSER) configuration option.

### 3.1.3 MINIMUM CODE WORDS

MTX[0..1] configuration bits selects the minimum number of code words that will be transmitted. If the button is released after 1.6 s (or greater) and MTX code words have been transmitted, the code word being transmitted will be terminated. The possible values are:

00 - 1

01 - 2

10 - 4

11 - 8

### 3.1.4 STATUS INFORMATION

The status bits will always contain the output of the Low Voltage detector (VLow), the Cyclic Redundancy Check (CRC) bits (or TIME bits depending on CTSEL) and the Button Queue information.

### 3.1.4.1 Low Voltage Detector Status (VLOW)

The output of the low voltage detector is transmitted with each code word. If VDD drops below the selected voltage, a logic '1' will be transmitted. The output of the detector is sampled before each code word is transmitted.

### 3.1.4.2 Button Queue Information (QUEUE)

The queue bits indicate a button combination was pressed again within 2 s after releasing the previous activation. Queuing or repeated pressing of the same buttons (or button combination) is detected by the rfHCS362 button debouncing circuitry.

The Queue bits are added as the last two bits of the standard code word. The queue bits are a 2-bit counter that does not wrap. The counter value starts at '00b' and is incremented if a button is pushed within 2 s of the previous button press. The current code word is terminated when the buttons are queued. This allows additional functionality for repeated button presses.

The button inputs are sampled every 6.4 ms during this 2 s period.

00 - first activation

01 - second activation

10 - third activation

11 - from fourth activation on

### 3.1.4.3 Time BITS

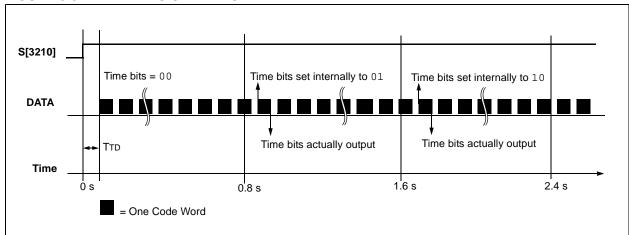

The time bits (Figure 3-5) indicate the duration that the inputs were activated:

00 - immediate

01 - after 0.8 s

10 - after 1.6 s

11 - after 2.4 s

The TIME bits are incremented every 0.8 s and will not wrap once it reaches '11'.

Time information is alternative to the CRC bits availability and is selected by the  $\mathtt{CTSEL}$  configuration bit.

### 3.1.4.4 Cyclic Redundancy Check (CRC)

The CRC bits are calculated on the 65 previously transmitted bits. The decoder can use the CRC bits to check the data integrity before processing starts. The CRC can detect all single bit errors and 66% of double bit errors. The CRC is computed as follows:

### **EQUATION 3-1:** CRC Calculation

$$CRC[1]_{n+1} = CRC[0]_n \oplus Di_n$$

and

$$CRC[\theta]_{n+1} = (CRC[\theta]_n \oplus Di_n) \oplus CRC[1]_n$$

with

$$CRC[1,0]_0 = 0$$

and  $Di_n$  the nth transmission bit  $0 \le n \le 64$

Warning: The CRC may be wrong when the battery voltage is near the selected VLow trip point. This may happen because VLow is sampled twice each transmission, once for the CRC calculation and once when VLow is transmitted. VDD tends to move slightly during a transmission which could lead to a different value for VLow being used for the CRC calculation and the transmission.

**Work around:** If the CRC is incorrect, recalculate for the opposite value of VLOW.

### FIGURE 3-6: CODE WORD DATA FORMAT

| With XSER = 0, CTSEL = 0           Status Information (5 bits)         Fixed Code Portion (32 bits)         Encrypted Portion (32 bits)           QUE 2 bits 2 bits 1-bit 2 bits 1-bit 4 bits 2 bits 1-bit 1-bit 4 bits 2 bits 1-bit 1                                                                                                                                            |          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Counter   Coun |          |

| QUE         CRC VLOW 2 bits         BUT 1-bit         SERIAL NUMBER (28 bits)         BUT Overflow 2 bits         DISC 10 bits         Synchron Overflow 16 bits           Q1         Q0         C1         C0         S2         S1         S0         S3         OVR1         OVR0           With XSER = 1, CTSEL = 0           Status Information (5 bits)         Fixed Portion (32 bits)         Encrypted Portion (32 bits)           QUE 2 bits 2 bits 1-bit         SERIAL NUMBER (32 bits)         BUT Overflow DISC 10 bits 15           Q1         Q0         C1         C0         C0 <td< td=""><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| With XSER = 1, CTSEL = 0  Status Information (5 bits)  QUE CRC 2 bits 2 bits 1-bit  Q1 Q0 C1 C0  With XSER = 1, CTSEL = 0  Fixed Portion (32 bits)  Fixed Portion (32 bits)  Encrypted Portion (32 bits)  Synchronic Counter Overflow 2 bits 10 bits 15  S2 S1 S0 S3 OVR1 OVR0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | nter     |

| Status Information (5 bits)  Fixed Portion (32 bits)  SERIAL NUMBER (32 bits)  Q1 Q0 C1 C0  Fixed Portion (32 bits)  Fixed Portion (32 bits)  SERIAL NUMBER (32 bits)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

| QUE CRC VLOW 2 bits 2 bits 1-bit SERIAL NUMBER (32 bits)  SERIAL NUMBER BUT Counter Overflow 2 bits 2 bits 10 bits 15  SYNChronic Counter Overflow 2 bits 10 bits 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

| QUE CRC VLOW 2 bits 2 bits 1-bit SERIAL NUMBER (32 bits)  SERIAL NUMBER BUT Counter Overflow 2 bits 2 bits 1-bit 15  Q1 Q0 C1 C0  S2 S1 S0 S3 OVR1 OVR0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ter      |

| With XSER = 0, CTSEL = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

| Status Information Fixed Portion (32 bits) Encrypted Portion (32 bits)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

| (5 bits)  QUE TIME VLow 2 bits 2 bits 1-bit 4 bits SERIAL NUMBER (28 bits)  Synchroni Counter Overflow DISC 16 bit 2 bits 10 bits 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ter      |

| Q1 Q0 T1 T0 S2 S1 S0 S3 S2 S1 S0 S3 OVR1 OVR0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| With XSER = 1, CTSEL = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

| Status Information (32 bits) Encrypted Portion (32 bits) (5 bits)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

| QUE TIME VLOW 2 bits 2 bits 1-bit SERIAL NUMBER (32 bits)  SERIAL NUMBER BUT Overflow 2 bits 2 bits 10 bits 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ter      |

| Q1 Q0 T1 T0 S2 S1 S0 S3 OVR1 OVR0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

| Transmission Direction LS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SB First |

### 3.2 LED Output

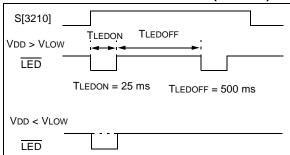

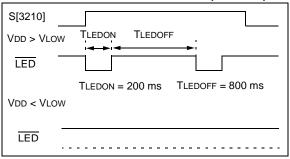

The LED pin will be driven LOW periodically while the rfHCS362 is transmitting data to power an external LED.

The duty cycle (TLEDON/TLEDOFF) can be selected between two possible values by the configuration option (LED).

FIGURE 3-7: LED OPERATION (LED = 1)

The same configuration option determines whether when the VDD Voltage drops below the selected VLOW trip point the LED will blink only once or stop blinking.

FIGURE 3-8: LED OPERATION (LED = 0)

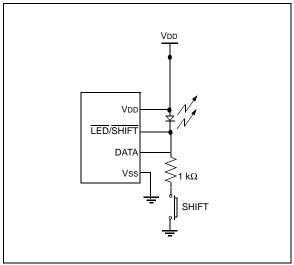

Note: When the rfHCS362 encoder is used as a Dual Encoder the LED pin is used as a SHIFT input (Figure 3-9). In such a configuration the LED is always ON during transmission. To keep power consumption low, it is recommended to use a series resistor of relatively high value. VLow information is not available when using the second Encryption Key.

### 3.3 Dual Encoder Operation

The rfHCS362G/362F contains two encryption keys (for example derived from two different Manufacturer's Codes), but only one Serial Number, one set of Discrimination bits, one 16-bit Synchronization Counter and a single 60-bit Seed value. For this reason the rfHCS362G/362F can be used as an encoder in multiple (two) applications as far as they share the same configuration: transmission format, baud rate, header and guard settings. The SHIFT input pin (multiplexed with the LED output) is used to select between the two encryption keys.

A logic 1 on the SHIFT input pin selects the first encryption key.

A logic 0 on the  $\overline{\text{SHIFT}}$  input pin will select the second encryption key.

FIGURE 3-9: USING DUAL ENCODER OPERATION

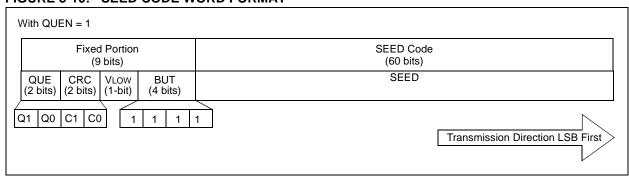

FIGURE 3-10: SEED CODE WORD FORMAT

### 3.4 Seed Code Word Data Format

A seed transmission transmits a unencrypted code word that consists of 60 bits of fixed data that is stored in the EEPROM. This can be used for secure learning of encoders or whenever a fixed code transmission is required. The seed code word further contains the function code and the status information (VLOW, CRC and QUEUE) as configured for normal code hopping code words. The seed code word format is shown in Figure 3-10. The function code for seed code words is always '1111b'.

Seed code words can be configured as follows:

- · Enabled permanently.

- · Disabled permanently.

- Enabled until the synchronization counter is greater than 7Fh, this configuration is often referred to as Limited Seed.

- The time before the seed code word is transmitted can be set to 1.6 s or 3.2 s, this configuration is often referred to as **Delayed Seed**. When this option is selected, the rfHCS362 will transmit a code hopping code word for 1.6 s or 3.2 s, before the seed code word is transmitted.

### 3.4.1 SEED OPTIONS

The button combination (S[3210]) for transmitting a Seed code word can be selected with the Seed and SeedC (SEED[0..1] and SEEDC) configuration options as shown in Table 3-1 and Table 3-2:

TABLE 3-1: SEED OPTIONS (SEEDC = 0)

|       | Seed          | 1.6 s Delayed Seed |

|-------|---------------|--------------------|

| SEED  | S[3210]       | S[3210]            |

| 00    | -             | -                  |

| 01    | 0101*         | 0001*              |

| 10    | 0101          | 0001               |

| 11    | 0101          | -                  |

| Note: | *Limited Seed |                    |

TABLE 3-2: SEED OPTIONS (SEEDC = 1)

|       | Seed          | 3.2 s Delayed Seed |

|-------|---------------|--------------------|

| SEED  | S[3210]       | S[3210]            |

| 00    | -             | -                  |

| 01    | 1001*         | 0011*              |

| 10    | 1001          | 0011               |

| 11    | 1001          | -                  |

| Note: | *Limited Seed |                    |

**Example A):** Selecting SEEDC = 1 and SEED = 11: makes SEED transmission available every time the combination of buttons S3 and S0 is pressed simultaneously, but Delayed Seed mode is not available.

**Example B):** Selecting SEEDC = 0 and SEED = 01: makes SEED transmission available only for a limited time (only up to 128 times). The combination of buttons S2 and S0 produces an immediate transmission of the SEED code. Pressing and holding for more than 1.6 seconds the S0 button alone produces the SEED code word transmission (Delayed Seed).

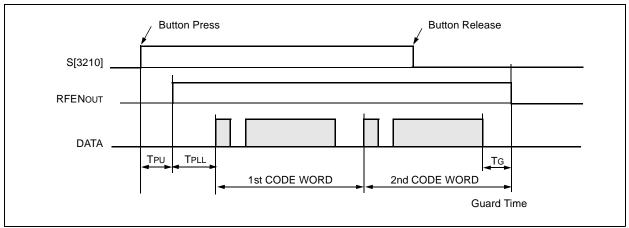

### 3.5 RF Enable and Transmitter Interface

The S3/RFENOUT pin of the rfHCS362 can be configured to function as an RF Enable output signal. This is selected by the RF Enable Output (RFEN) configuration option as described in Section 4.5.13. When enabled, this pin will be driven HIGH before data is transmitted through the DATA pin.

The RFENOUT and DATA pins are synchronized to interface with the transmitter. Figure 3-11 shows the start-up sequence. A button is debounced and the EEPROM counter advanced during the power-up delay (TPU). Then the RFENOUT pin goes high to enable the transmitter. The DATA output is delayed to give the

transmitter crystal oscillator and PLL time to startup (TPLL). The RFENout signal will go LOW one guard time after the end of the last code word.

When the RF Enable output is selected, the S3 pin can still be used as a button input. However, only minimum code words will be transmitted. An alternative solution for more than three push buttons can be the switching diode circuit described in Section 1.2.

In typical implementations of the rfHCS362G/362F, the encoder RFENout pin is connected to the transmitter RFENIN pin.

FIGURE 3-11: PLL INTERFACE

# 4.0 EEPROM MEMORY ORGANIZATION

The rfHCS362G/362F contains 288 bits (18 x 16-bit words) of EEPROM memory (Table 4-1). This EEPROM array is used to store the encryption key information and synchronization value. Further descriptions of the memory array is given in the following sections.

TABLE 4-1: EEPROM MEMORY MAP

| Word<br>Address | Field    | Description                            |

|-----------------|----------|----------------------------------------|

| 0               | KEY1_0   | 64-bit Encryption Key1<br>(Word 0) LSB |

| 1               | KEY1_1   | 64-bit Encryption Key1<br>(Word 1)     |

| 2               | KEY1_2   | 64-bit Encryption Key1<br>(Word 2)     |

| 3               | KEY1_3   | 64-bit Encryption Key1<br>(Word 3) MSB |

| 4               | KEY2_0   | 64-bit Encryption Key2<br>(Word 0) LSB |

| 5               | KEY2_1   | 64-bit Encryption Key2<br>(Word 1)     |

| 6               | KEY2_2   | 64-bit Encryption Key2<br>(Word 2)     |

| 7               | KEY2_3   | 64-bit Encryption Key2<br>(Word 3) MSB |

| 8               | SEED_0   | Seed value (Word 0)<br>LSB             |

| 9               | SEED_1   | Seed value (Word 1)                    |

| 10              | SEED_2   | Seed value (Word 2)                    |

| 11              | SEED_3   | Seed value (Word 3)<br>MSB             |

| 12              | CONFIG_0 | Configuration Word<br>(Word 0)         |

| 13              | CONFIG_1 | Configuration Word<br>(Word 1)         |

| 14              | SERIAL_0 | Serial Number<br>(Word 0) LSB          |

| 15              | SERIAL_1 | Serial Number<br>(Word 1) MSB          |

| 16              | SYNC     | Synchronization counter                |

| 17              | RES      | Reserved – Set to zero                 |

# 4.1 KEY\_0 - KEY\_3 (64-bit Encryption Key)

The 64-bit encryption key is used to create the encrypted message. This key is calculated and programmed during production using a key generation algorithm. The key generation algorithm may be different from the KEELOQ algorithm. Inputs to the key generation algorithm are typically the transmitter's serial number and the 64-bit manufacturer's code. While the key generation algorithm supplied from Microchip is the typical method used, a user may elect to create their own method of key generation.

### 4.2 SYNC (Synchronization Counter)

This is the 16-bit synchronization value that is used to create the hopping code for transmission. This value will be incremented after every transmission.

# 4.3 SEED\_0, SEED\_1, SEED\_2, and SEED 3 (Seed Word)

This is the four word (60 bits) seed code that will be transmitted when seed transmission is selected. This allows the system designer to implement the secure learn feature or use this fixed code word as part of a different key generation/tracking process or purely as a fixed code transmission.

**Note:** Upper four Significant bits of SEED\_3 contains extra configuration information (see Table 4-5).

### 4.4 SERIAL\_0, SERIAL\_1 (Encoder Serial Number)

SERIAL\_0 and SERIAL\_1 are the lower and upper words of the device serial number, respectively. There are 32 bits allocated for the serial number and a selectable configuration bit determines whether 32 or 28 bits will be transmitted. The serial number is meant to be unique for every transmitter.

TABLE 4-2: CONFIG\_0

| Bit<br>Address | Field    | Description            | Values                                                                                                        |  |

|----------------|----------|------------------------|---------------------------------------------------------------------------------------------------------------|--|

| 0              | OSC_0    | Oscillator adjust      | 0000 - nominal                                                                                                |  |

| 1              | OSC_1    |                        | 1000 - fastest<br>0111 - slowest                                                                              |  |

| 2              | OSC_2    |                        | OTIT - Slowest                                                                                                |  |

| 3              | OSC_3    |                        |                                                                                                               |  |

| 4              | VLOW_0   | VLOW select            | nominal values                                                                                                |  |

| 5              | VLOW_1   |                        | 000 - 2.0V 100 - 4.0V                                                                                         |  |

| 6              | VLOW_2   |                        | 001 - 2.1V 101 - 4.2V<br>010 - 2.2V 110 - 4.4V<br>011 - 2.3V 111 - 4.6V                                       |  |

| 7              | BSEL_0   | Bit rate select        | 00 - TE = 100 μs                                                                                              |  |

| 8              | BSEL_1   |                        | 01 - TE = 200 μs<br>10 - TE = 400 μs<br>11 - TE = 800 μs                                                      |  |

| 9              | MTX_0    | Minimum number of code | 00 - 1                                                                                                        |  |

| 10             | MTX_1    | words                  | 01 - 2<br>10 - 4<br>11 - 8                                                                                    |  |

| 11             | GUARD_0  | Guard time select      | 00 - 0 ms (1 TE)                                                                                              |  |

| 12             | GUARD_1  |                        | 01 - 6.4 ms + 2 TE<br>10 - 25.6 ms + 2 TE<br>11 - 76.8 ms + 2 TE                                              |  |

| 13             | TIMOUT_0 | Time-out select        | 00 - No Time-out                                                                                              |  |

| 14             | TIMOUT_1 |                        | 01 - 0.8 s to 0.8 s + 1 code word<br>10 - 3.2 s to 3.2 s + 1 code word<br>11 - 25.6 s to 25.6 s + 1 code word |  |

| 15             | CTSEL    | CTSEL                  | 0 = TIME bits<br>1 = CRC bits                                                                                 |  |

### 4.5 Configuration Words

There are 36 configuration bits stored in the EEPROM array. They are used by the device to determine transmission speed, format, delays and Guard times. They are grouped in three Configuration Words: CONFIG\_0, CONFIG\_1 and the upper nybble of the SEED\_3 word. A description of each of the bits follows this section.

### 4.5.1 OSC

The internal oscillator can be tuned to  $\pm 10\%$ . (0000 selects the nominal value, 1000 the fastest value and 0111 the slowest). When programming the device, it is the programmer's responsibility to determine the optimal calibration value.

### 4.5.2 VLOW[0..2]

The low voltage threshold can be programmed to be any of the values shown in Table 4-2.

### 4.5.3 BSEL[0..1]

The basic timing element TE, determines the actual transmission Baud Rate. This translates to different code word lengths depending on the encoding format selected (Manchester or PWM), the Header length selection and the Guard time selection, from approximately 40 ms up to 220 ms. Refer to Table 4-2 for bit rate configuration. Refer to Figure 10-3 through Figure 10-6 for code word timing.

### 4.5.4 MTX[0..1]

MTX selects the minimum number of code words that will be transmitted. A minimum of 1, 2, 4 or 8 code words will be transmitted.

Note: If MTX and BSEL settings in combination require a transmission sequence to exceed the TIMOUT setting, TIMOUT will take priority.

TABLE 4-3: CONFIG\_1

| Bit<br>Address | Field  | Description            | Values                                                                                                                                                                             |

|----------------|--------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0              | DISC_0 | Discrimination bits    | DISC[9:0]                                                                                                                                                                          |

| 1              | DISC_1 |                        |                                                                                                                                                                                    |

| 2              | DISC_2 |                        |                                                                                                                                                                                    |

|                |        |                        |                                                                                                                                                                                    |

| 8              | DISC_8 |                        |                                                                                                                                                                                    |

| 9              | DISC_9 |                        |                                                                                                                                                                                    |

| 10             | OVR_0  | Overflow               | OVR[1:0]                                                                                                                                                                           |

| 11             | OVR_1  |                        |                                                                                                                                                                                    |

| 12             | XSER   | Extended Serial Number | 0 - Disable<br>1 - Enable                                                                                                                                                          |

| 13             | SEEDC  | Seed Control           | 0 = Seed transmission on:<br>S[3210] = 0001 (delay 1.6 s)<br>S[3210] = 0101 (immediate)<br>1 = Seed transmission on:<br>S[3210] = 0011 (delay 3.2 s)<br>S[3210] = 1001 (immediate) |

| 14             | SEED_0 | Seed options           | 00 - No Seed                                                                                                                                                                       |

| 15             | SEED_1 |                        | <ul> <li>01 - Limited Seed (Permanent and Delayed)</li> <li>10 - Permanent and Delayed Seed</li> <li>11 - Permanent Seed only</li> </ul>                                           |

### 4.5.5 GUARD

The Guard time between code words can be set to 0 ms, 6.4 ms, 25.6 ms and 76.8 ms. If during a series of code words, the output changes from Hopping Code to Seed the Guard time will increase by 3 x Te.

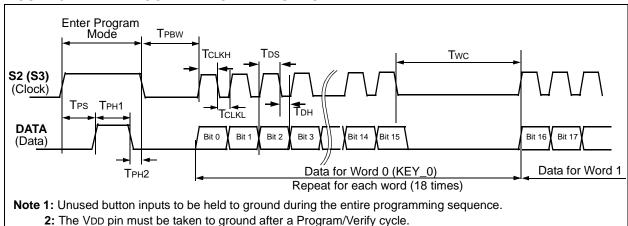

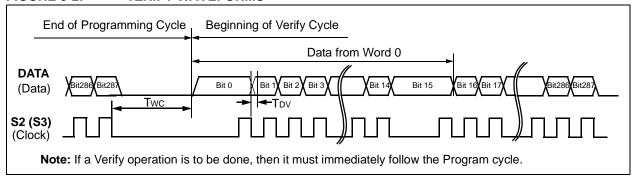

### 4.5.6 TIMOUT[0..1]